# **EDWinXP – An Integrated EDA Software Package**

**EDWinXP** (Electronic Design For Windows) is a CAD/CAE Software package of seamlessly integrated, task oriented modules covering all stages of the electronic circuit design process-from capturing the idea of a circuit in the form of schematic diagram to generate a full set of documentation for manufacturing and assembly of PCBs. Additionally the package includes various validation tools ensuring correctness and integrity of designed circuits. Complete design information is stored in the integrated project database, simultaneously accessible by schematic diagram editor, analog/digital, mix-mode circuit simulator, PCB layout editor, board level analysis and fabrication output managers. Front and back annotation of all design changes is fully automatic. EDWinXP comes with extensive part library which may be updated, customized and enhanced with the help of library editor.

## Modules (EDWinXP ver. 1.70)

- > Schematic Editor

- Library Editor

- Mixed Mode Simulator

- EDSpice Simulator (SPICE based simulator)

- 8051 Microcontroller Kit

- > AVR Kit

- > PIC Microcontroller Kit

- VHDL Co-Simulation and Model Generators

- PCB Layout Editor

- > Thermal Analyzer

- Electromagnetic Analyzer

- > Field Analyzer

- Signal Integrity Simulation

- Fabrication Manager

- > 3D Editors and Viewers

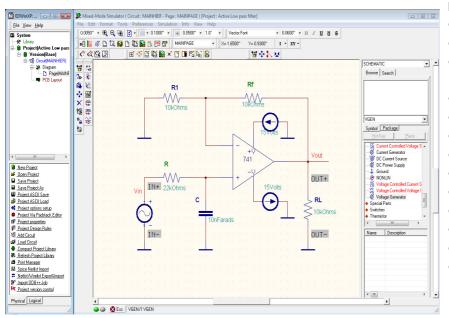

# **Schematic Diagram Editor:**

The schematic diagram editor contains a full set of manual and automated tools for placement of circuit elements on the diagram and for routing the connection. Additional graphical and textual information may be created in the form of design notes.

### **Features:**

- Top down hierarchical circuits (99)

- Customizable component browser

- Definable connection and bus width

- Intelligent and interactive routing

- Auto packaging

- Instant packaging

- Smart auto placer

- Circuit DRC

- Filter designer

- Page/design notes

- Block diagram elements

- Truth table to diagram converter

- VHDL code to diagram converter

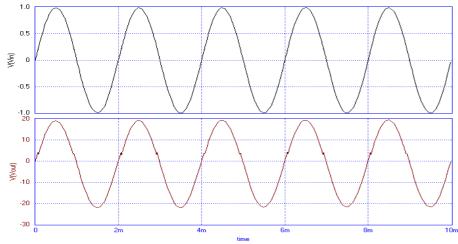

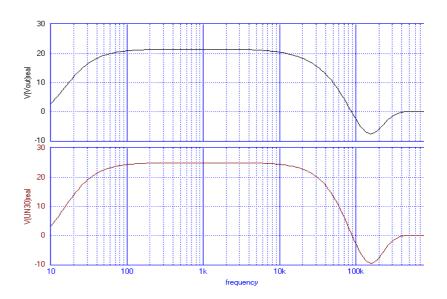

### **Circuit Simulator:**

The functioning of the circuit may be tested with the help of integrated simulators in EDWinXP. Mixed mode simulator, the system's native circuit level analyzer and EDSpice, the full implementation of XSPICE as defined by Georgia Tech are two simulators in EDWinXP.

Mixed mode simulator supports TD, DC, AC, Parameter sweep, Fourier, Monte Carlo and sensitivity analyses of analog, digital, and mixed-signal circuits.

#### **Features:**

- Mixed mode Simulator

- EDSpice Simulator

- Logic Analyzer

- Multi channel Oscillograph

- EDSpice interactive Interpreter

- Circuit File Editor

- Instant Probes

- Model Generators

- VHDL to SPICE Model

- VHDL to Mixed Mode

## **SPICE Net list Generation from schematic:**

Active low pass filter (Netlist View)

```

*

V9 0 7 15

V8 6 0 15

R7 0 4 10k

R5 1 0 10k

X1 8 1 6 7 4 TL032_30

C2 0 8 10n

V3 5 0 AC SIN ( 0 1 100k 0 0 )

R4 4 1 10k

R6 8 5 22k

*CODE MODEL DEFINITIONS

```

.END

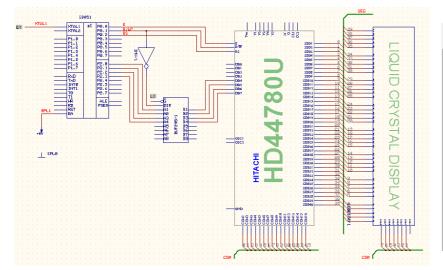

### Microcontroller simulation kit:

The Kit contains project databases designed to illustrate functionality of 8051, AVR AT 90S2313, PIC16C5X, and PIC16X84. It uses MMI technology that enables edition and compilation of programs in C and assembly language, and it also allows debugging the code in real time. The kit contains series of instrumental models such as memories, interrupt generators, serial/parallel pattern generators, 7-segment displays etc. for generating parallel and serial binary data patterns and asynchronous hardware interrupts.

```

CEditor | Assembler Editor | Listing View | Hex Editor (ROM) | Hex Editor (EEPROM) | Disassembler | Output

void Delay (int Time);

int Busy (void);

void Command (int Value);

void Display (int Value);

void eeprom_write (unsigned char Address, unsigned char Data);

unsigned char eeprom_read (unsigned char Address);

void init (void)

{

_asm

_config _LP OSC

org 0x2100

DE "EDWinXP-Ver 1.50"

org 0x0005

_endasm;

}

void main (void)

{

```

# **VHDL Editor and Complier:**

VHDL source files (Level 0 syntax) may be created with VHDL editor. This may then be complied and imported to EDWinXP as a project. This project may then be exported to netlists of the format CUPL, XILINX, JEDEC etc.

```

File Edit Compile View

library ieee;

use ieee.std_logic_1164.all;

entity VHDLTemplate is port (

i0 : in std_logic;

: in std_logic;

: in std_logic;

: in std_logic;

: in std_logic;

: out std_logic;

: out std_logic;

00

end VHDLTemplate;

architecture VHDL_Template of VHDLTemplate is

--Paste your code here

01 <=

(i0 or i2) and i3;

end VHDL_Template;

Errors Found in VHDL File - VHDLNetlist.vhd

Line: 19, Error: Semicolon expected

```

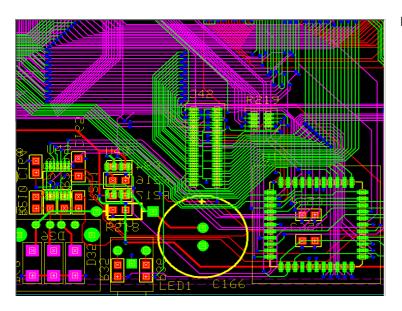

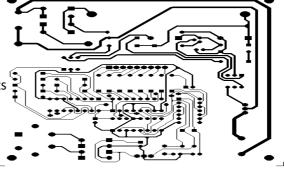

## **PCB Layout Editor:**

EDWinXP project supports design of 32-layer boards. Components are created automatically as a result of packaging executed while editing the schematic diagram of the circuit. Location and orientation of components is defined either by manual relocation to desired position or with the help of the auto placer.

Traces may be routed manually with automatic via insertion whenever a routing layer is changed. Sixteen types of user defined via pads are supported. A dedicated "full board" auto router module is integrated with the PCB layout editor. Insertion of air gaps and the thermal pads on artworks is automatic. Design rules violation, clearance errors and missing or incomplete connections are also detected automatically.

All changes introduced in the circuit design are automatically back annotated to schematic diagram.

### Features:

- 32 layers

- Smart auto placer

- Auto router

- Online trace clearance check

- Trace length and width trimming

- DRC

- Test point

- Connection check

- Automatic correction of selected clearance errors

- Automatic clearance correction after routing and rerouting

- Through holes and buried vias

- 3D view of layout

# **Board Analyzers:**

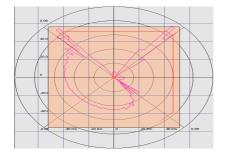

### Thermal analyzer

The temperature distribution on a finished PCB may Be analyzed graphically with the help of thermal Analyzers. The result of the analysis is displayed using Isotherms or color mapping schemes.

# Unit: % 120.40 114.04 114.04 107.68 101.78 94.96 0...01 75.88 69.52 0...01 50.44 44.03 97.72 31.36 25.00

## **Electromagnetic field analyzer**

Electromagnetic analyzer presents graphically the Predicted intensity of electromagnetic Fields inside and Outside board boundaries.

The signal integrity analyzer detects distortion Noise and Crosstalk for critical signals.

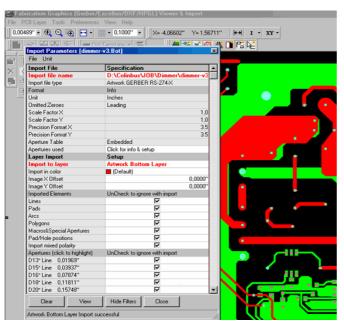

# **Fabrication Manager:**

All CAM function of EDWinXP are grouped in this module. The User has the option to add targets, coupons, thieving and Venting areas. Copper pour areas are checked for possible shorts Or area isolated by air gaps. Automatic or manual copper Removal is also implemented. Final artworks are prepared for Photo plotting.

## **Exports:**

**ODB++ Export**

DXF output

EDIF version 2.0

Export CNC data in G-CODE

Spectra and maxroute auto routers

Xilinx netlist

JEDEC netlist

GERBER and many others.....

### Imports:

ODB++ import

DXF

SPICE netlist (SPICE3F5 & XSPICE)

VHDL (Level '0' syntax)

Geber ASCII (Reverse Engg)

Orcad PCB II wirelist and many others......

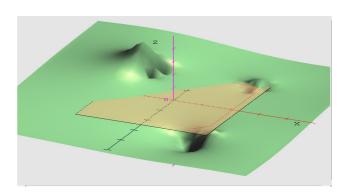

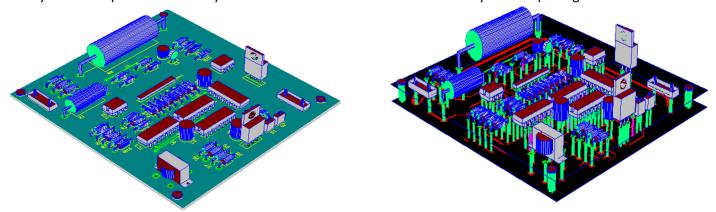

### 3D Editor and viewer:

EDWinXP may present designed PCB in "real life" three dimensional views. In order to make it possible, 3D views of component packages (created according to IPC, JEDEC and EIA standards.) are included in the system part library. Tools are provided in library editor to create and edit 3D views for newly created packages.

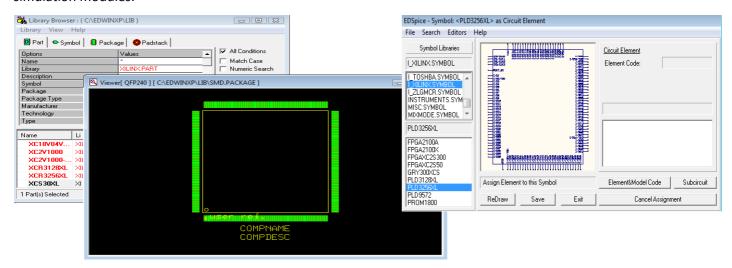

# **Library Editor:**

EDWinXP component libraries may be updated, customized or enhanced with the help of library editor. Functionality of this module allows definition of graphical representation of components in schematic diagram (symbol editor) and on printed circuit board (package Editor). These elements are included then in the component description, which also contains the packaging information, thermal parameters and link to simulation modules.

### **List of Material Editor:**

List of material editor generates customized bill of material that can be imported to excel for further processing.

# **Project Version Control:**

Keep track the changes in EDWinXP projects.

| International Customers List |                                                 |

|------------------------------|-------------------------------------------------|

| Volvo, Sweden                | Industry Electronics, Czech Republic            |

| Ericsson, Sweden             | Software Sistemas Especializados Ltda, Colombia |

| Nokia, Sweden                | Elecsys, Korea                                  |

| Siemens, Sweden              | VESL Technologies, Tanzania                     |

| Alkatel, Sweden              | Test & Rework Solutions (Pty) Ltd, South Africa |

| Bofors, Sweden               | Swifteurotech, U.K                              |

| FCC (US FCC authority)       | Whingate, U.K                                   |

| PCB Technologies, Italy      | Toyota, Japan                                   |

| Delta Control Systems Canada |                                                 |

Unicraft, Japan Technologia Tecom S.L, Spain R.K System, Poland West Test, Germany Mercure Telecom, France Jeppson, Sweden

### Commercial customers in India

DRDO, Bangalore

DRDE, Gwalior, Madhya Pradesh

HAL, Bangalore

TATA Institute of Fundamental Research, Mumbai

CDAC, Bangalore

### PARTIAL LIST OF EDUCATIONAL INSTITUTES USING EDWINXP IN INDIA

limt Engineering College, Greater Noida limt Engineering College, Meerut Iilm Academy For Higher Learning Greater Noida G.L.Bajaj ,Greter Noida Kngd, Ghaziabad H.R.Inst, Ghaziabad Rkgit, Ghaziabad R. D. Engineering College, Ghaziabad Lord Krishana College Of Engineering Krishna Engineering College, Ghaziabad Srm University Modinagar Campus. Chhattisgarh Institute Of Technology, Chhattisgarh M.M. Foundation, Raipur, Chhattisgarh Jaipur Engineering College, Jaipur, Rajasthan Global Institute Of Technology, Jaipur Kiit, Gurgaon World Inst Of Tech, Gurgoan Koustuv Inst Of Self Domain, Bhubhneshwar College Of Engg ,Bhubhneshwar Bit Institute Of Technology - Hindupur Nitte College Of Engineering - Bangalore Dr. Ambedkar Institute Of Technology - Bangalore Dayanand Sagar College Of Engineering - Bangalore Arunai Engineering College - Thiruvannamalai Sir M. Visvesvaraiha Institute Of Technology - Bangalore Bapuji College Of Engineering - Davanagere Cummins College Of Engineering For Women – Pune Dr. D.Y.Patil Women's College Of Engineering - Pune Singhad College Of Engineering, Pune A.I.T. College - Pune Genba Sopanrao Moze Engineering College, Pune Dr Dy Patil Institute, Akurdi, Pune Dr Dy Patil Institute, Pimpri, Pune B.V. Bhoomaraddi College Of Engg & Tech, Hubli Regency Institute Of Technology, Pondicherry Dr. Samuel George Institute Of Engg & Tech, Markapur

Sri Venkateswhara College Of Engg & Tech, Chittoor

Indira Educational And Charitable Trust, Chennai

Anjuman Institute Of Technology, Bhatkal

Gm Institute Of Technology, Davangere

Vemana Institute Of Technology, Bangalore Motichand Lengade Bharatesh Polytechnic, Belgaum Jatipita Engineering College, Adilabad M.G.R. Engineering College, Chennai Nmam Institute Of Technology - Nitte Vel Multimedia College, Chennai Sree Sastha Institute Of Engg & Tech, Chennai Govt. College Of Engg, Sreekrishnapuram, Palakkad Marian Engineering College, Kazhakootam, Trivandrum L.B.S. Inst. Of Tech For Women, Poojappura, Trivandrum Govt. Engineering College, Barton Hill, Trivandrum Mohandas College Of Engg And Tech., Trivandrum Viswajyothi College Of Engineering, Ernakulam Rajagiri School Of Engg & Tech, Kakkanad, Cochin Sree Narayan Gurukulam College Of Engg., Ernakulam Saintgits College Of Engg, Kottukulam Hills, Pathamuttom Sree Buddha College Of Engg. Pattoor P.O. Alapuzha St. Joseph's College Of Engg. & Tech., Kottayam Musaliar College Of Engg. & Technology, Pattanamthitta Younus College Of Engg. & Tech., Vadakkevila, Kollam Mary Matha College Of Engg. & Tech., Neyyattinkara Travancore College Of Engineering, Kollam P.A. Aziz College Of Engg & Tech., Karakulam Basilous Mathews Ii College Of Engg, Kollam University College Of Engg. Kariavattom, Trivandrum Mar Baselious College Of Engineering, Peermade Idukki College Of Engineering, Chengannur, Alappuzha Model Engineering College, Thrikkakara, Kochi Caarmel Engg. College, Koonmkara, Pathanamthitta Jyothi Engineering College, Vettikkattiri, Thrissur Es College Of Engineering, Thrissur Oyal Engineering College, Thrissur Vidya Academy Of Science And Technology, Thrissur Nehru College Of Engg. & Research Centre, Thrissur Adiparashakti College Of Engg. – Tamilnadu S K R Engineering College - Chennai A V C College - Mayiladuturai Prathyusha Institute Of Tech & Mgt, Thiruvallur Saveetha Engineering College, Chennai Shri Andal Alagar College Of Engineering, Mamandu

| ٠. | • |    |       | • |   | • | • | ۰ | ۰ | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • | • | • | • | • | • | • | • |  |  |   | • | • | • |  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • |  | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | ۰ | • | • | <br>• |  |  |

|----|---|----|-------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|---|---|---|---|---|---|---|--|--|---|---|---|---|--|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|--|---|--|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|---|---|-------|--|--|

|    | • | ٠. | <br>• |   | • | • |   |   |   | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • | • | • | • | • | • | • | • |  |  | • | • | • | • |  | • | • | • | • | • | • | • | • | • | • | • | • | • | • | • |  | • |  | • | • | • | • | • | <br>• | • | • | • | • | • | • | • | ۰ | • | • | <br>• |  |  |